以下筆記參考了如下幾本書 :

- 數位邏輯設計附實習 第三版 (楊豐瑞, 陳福春, 旗標出版)

- 最新數位邏輯電路設計 第三版 (劉紹漢等, 全華全華)

- 數位邏輯設計 第三版 (黃慶璋, 全華出版)

以下會用到的標準 TTL IC 規格與接腳圖參考 :

# http://www.nteinc.com/specs/7400to7499/pdf/

# http://dw.hanbit.co.kr/exam/1600/AppendixB_TTL_IC_Databook.PDF

序向邏輯課程基本上依序可分成下列四大部分 :

- Latch 與 Flip-Flop (正反器)

- Register (暫存器)

- Counter (計數器)

- Finite State Machine (有限狀態機)

序向邏輯電路的基本元件是 Latch (電栓) 與 Flip-Flop (正反器), 其中正反器是主角, 大部分應用都採用正反器, Latch 由於有 Racing 問題要避開較少用. 正反器中又以 JK 與 D 正反器最常用, T 正反器可由 JK 正反器製作, 因此標準 TTL IC 中可找到許多 JK 與 D 正反器, 找不到 T 正反器.

基本的 Latch 可用兩個 NAND 閘來建構, 稱為 NAND Latch, 這是 Active low 邏輯 (low 啟動) 電栓, 因此兩個輸入 /S 與 /R 前面有個 /, 亦即低態時設置 (set, Q=1) 或重設 (reset, /Q=1), 其電路結構與功能表 (function table) 如下 :

也可以用兩個 NOR 閘來建構, 稱為 NOR Latch, 這是 Active high 邏輯 (high 啟動) 電栓, 亦即高態時設置 (set, Q=1) 或重設 (reset, /Q=1), 其電路結構與功能表 (function table) 如下 :

可見不論是 NAND 或 NOR latch, 其電路組態都是以交互回授 (cross feedback) 來組成所謂的雙穩態 (bi-stable) 結構, 兩個輸出 (Q, /Q) 基本上會在 0 與 1 之間切換狀態 (set 或 reset) 或者保存狀態 (No change), 此特性讓 Latch 具有記憶 (memory) 的功能.

不過四個輸出狀態中有一個是不允許的狀態 (not allowed), 對於 NAND latch 來說 /S=0 與 /R=0 是不允許的輸入, 因為這會強迫 Q 與 /Q 都進入 high (1) 狀態; 而對於 NOR latch 來說 S=1 與 R=1 是不允許的輸入, 因為這會強迫 Q 與 /Q 都進入 high (1) 狀態, 這不允許的狀態除了會讓 Q 與 /Q 失去反相對比的功能外, 當離開此狀態時還會出現邏輯閘的競賽現象 (racing), 導致 Q 與 /Q 的狀態無法預測.

對於 NAND latch 而言, 當 /S=0 與 /R=0 時 Q 與 /Q 都會進入 high (1) 狀態; 若 /S 與 /R 同時回到 high(1), 則兩個 NAND 閘照理都要輸出 0, 不過這時反應較快的 NAND 在輸出 0 後會回授去抑制另一個 NAND 閘使其仍輸出 1, 於是兩個 NAND 就像是在比賽一樣, 所以稱為 Racing 現象. 由於哪一個反應會較快是無法預測的, 導致 Q 與 /Q 狀態無法預測, 因此 /S=0 與 /R=0 對 NAND latch 是不允許的輸入, 如下面波形圖所示 :

同樣地, 對於 NOR latch 而言, 當 S=1 與 R=1 時 Q 與 /Q 都進入 low (0) 狀態, 當 S 與 R 同時回到 0 時, 兩個 NOR 閘都要輸出 1, 反應較快的 NOR 在輸出 1 後會回授抑制另一個 NOR 閘使其仍輸出 0. 由於哪一個反應會較快是無法預測的, 導致 Q 與 /Q 狀態無法預測, 因此 S=1 與 R=1 對 NOR latch 來ㄕㄨㄛ是不允許的輸入, 如下面波形圖所示 :

競賽情況下何者勝出取決於邏輯閘電路的傳遞延遲 (propagation delay), 這是邏輯閘從輸入變化到輸出改變狀態所需要的時間延遲, 有 TPLH 與 TPHL 兩種, 分別表示輸出從 Low 變 High 以及從 High 變 Low 所需的時間 :

例如標準 TTL IC 中 7400 是一顆包含 4 個 NAND 閘的 IC, 從規格書 (data sheet) 中可查知其 TPLH 典型值為 9 ns; 而 TPHL 典型值為 10 ns :

參考 NTE 公司的 74LS00 規格書 :

# http://www.nteinc.com/specs/7400to7499/pdf/nte74LS00.pdf

如果用 7400 來製作 NAND latch, 則競賽的結果就要看哪一個 NAND 閘的 TPHL 延遲較短. 相反地, 如果使用 NOR 閘來製作 latch, 則競賽結果就要看哪一個 NOR 閘的 TPLH 較短.

下面範例使用一個 7400 來製作 NAND latch, 使用其中的兩個來建構 latch, 另外兩個則用來做成反相器, 以便將 active low 的 /S 與 /R 輸入轉成 active high 的 S 與 R :

其等效電路圖與範例波形圖如下 :

可見經過前置反相器後, 此 latch 電路的 function table 變成與 NOR latch 一樣 (等於一個 NOR latch, 事實上它們是等效的), 亦即 S=1 與 R=1 為不允許的輸入. 所以以下將一律用 NAND 閘來製作 latch.

也有現成的 NAND latch 標準 IC 可用, 例如 74279 便是一個含有 4 個 NAND latch 的 IC, 其接腳與電路圖如下 :

可見由於接腳數的限制此 IC 並未將 /Q 接出. 參考 :

# http://www.nteinc.com/specs/7400to7499/pdf/nte74LS279.pdf

上面不管是 NAND 或 NOR latch, 輸入信號 S, R 或 /S, /R 都要小心不要同時為 1 (NOR latch) 或同時為 0 (NAND latch) 以避免競賽問題. 是否可以將此限制局限於一個較為短暫的時間內而不是整個時間軸呢?

從上面 7400 這個例子可以獲得一個啟發, 我們可以將第一級的 NAND 閘各取出一個輸入接在一起成為控制輸入 C, 只有在控制輸入 C=1 時 S 與 R 才能獲准進入 NAND latch, 此期間內 S 與 R 才需要避免同時為 high(1), 在 C=0 時 S 與 R 則不受限制, 稱為 Gated NAND lantch 或 Controlled NAND latch :

從 function table 可知, 此受控之 latch 有兩個 no change 情況, 當 C=0 時, 第一級的兩個 NAND 閘都輸出 1 使得後級的 NAND latch 保存目前狀態不變. 另一個 no change 情況是 C=1 且 S=R=1, 同樣使第一級 NAND 閘都輸出 1 而讓後級的 NAND latch 保存目前狀態不變, 範例波形圖如下 :

這個控制輸入 C 其實就是後面要介紹的時鐘信號 (clock) 雛形, 這是驅動同步系統運作的心跳 (heartbeat).

不過上面這個 Gated SR latch 還是有不允許的輸入 C=R=S=1 存在, 雖然已經被限縮在 C=1 期間, 但仍有發生競賽情況的可能. 避免這種情況的一個辦法是利用反相器讓進入第一級 NAND 閘的輸入永遠不會同時為 high (1), 這種 latch 稱為 Gated D latch 或 Controlled D latch :

從 function table 可知當 C=0 時第一級 NAND 閘都被迫輸出 high (1), 所以不管 D 輸入甚麼, 後級的 NAND latch 都不受影響, 而保存現在的狀態. 當 C=1 時, 第一級 NAND 閘都被致能, 若 D=0, 則 /S=1, /R=0, 後級的 NAND latch 被重置為 Q=0. 反之若 D=1, 則 則 /S=0, /R=1, 後級的 NAND latch 被設置為 Q=1, 範例波形圖如下 :

可見 D latch 已經徹底消除了競賽情況.

常用的 D latch IC例如 7475, 此 IC 包含四個 D latch, 但可能是接腳數目限制, 其控制輸入是兩兩一組共用一個, 亦即只有兩個控制輸入 Enable1-2與 Enable3-4, 其接腳圖如下 :

參考 :

# http://www.nteinc.com/specs/7400to7499/pdf/nte74LS75.pdf

上面所介紹的 latch 全部都是運作在 high-low 位準上, 其實這也是分別 latch 與 flip-flop 的關鍵, 亦即 :

- latch : 以輸入信號的位準觸發記憶狀態改變

- flip-flop : 以輸入信號的變化 (上升下降) 觸發記憶狀態改變

如何偵測信號的上升 (rising) 與下降 (falling 或 trailing) 緣呢 ? 最簡單的偵測電路是利用 propagation delay 原理來製作, 偵測上升緣的邏輯電路如下 :

此電路利用一個反相器產生 /CLK 信號, 此反相信號需要一個 NOT 閘的傳遞延遲時間才會到達 AND 閘輸入端, 於是兩個輸入只有一個 NOT 閘 TPHL 的期間同時為 high (1), 因此 AND 的結果產生寬度為一個 NOT 閘 TPHL 的脈衝, 它標誌著 CLK 信號的上升緣.

只要將上升緣偵測電路中的 AND 閘改成 NOR 閘即變成偵測下降緣的邏輯電路, 如下圖所示 :

此電路的反相器傳播延遲使得進入 NOR 閘的信號不同時, 而 NOR 閘只在兩個輸入均為 low (0) 時才會輸出 high (1), 因此會在 CLK 的下降緣附近產生一個寬度為 NOT 傳遞延遲時間 TPLH 的正脈衝.

利用此傳遞延遲現象製作之上下緣脈衝產生器就可用來建構最簡單的 D 正反器 (D flip-flop), 其電路圖, 功能表, 以及範例波形圖如下 :

可見 CLK 信號經過上升緣偵測電路後產生一個傳遞延遲寬度的脈波 C, 此脈波的 high 位準部分會讓 D 輸入通過第一級 NAND 進入後級的 NAND latch 中儲存, 所以 Q 與 /Q 輸出都是在 CLK 的上升緣才會轉變狀態, 這是同步系統的基礎. D flip-flop 中的邊緣偵測器若改為下降緣偵測電路的話, 則 Q 與 /Q 將於 CLK 的下降緣才會轉變狀態, 這種正反器會在 CLK 輸入端以一個小圓圈表示, 如下圖所示 :

從 D 正反器的 function table 可知, D 輸入值會在 CLK 上升緣的時候被存入 Q 中, 而在 CLK=0, 1 或下降緣時維持狀態不變 (不動作), 亦即 D flip-flop 主要是工作在 set 與 reset 兩種狀態, 若聚焦於輸入輸出關係, 其 function table 可摘要成下表 :

其中 Qn+1 表示 D 正反器的下一個狀態 (next state) 等於 D 輸入. 通常我們用 Qn 表示現在的狀態 (present state); 而用 Qn+1 表示下一個狀態 (next state).

除了被 CLK 同步的輸入信號外, 正反器還有兩個常見的輸入 : /PRE 與 /CLR, 其中 /PRE 用來預設 (preset) 正反器輸出 Q 為 high (1); 而 /CLR 則用來重設 (reset) 正反器輸出 Q 為 low (0). 它們通常是 active low (低態動作) 且為非同步輸入 (立即影響輸出), 電路圖如下 :

從 function table 可知, /PRE 與 /CLR 不可以同時為 low (0), 因為對 NAND latch 而言會造成 racing 競賽現象. 當 /PRE=0 且 /CLR=1 時, 不管輸入 D 與 CLK 為何, 輸出 Q 會被預設為 high (1); 當 /PRE=1 且 /CLR=0 時, 不管輸入 D 與 CLK 為何, 輸出 Q 會被重設為 low (0). 其餘與上面 D 正反器的功能相同, 範例波形圖如下 :

含 /PRE 與 /CLR 的 D 正反器電路符號如下所示, 左邊為上升緣動作, 右邊則為下降緣動作 :

標準 TTL IC 中常見的 D 正反器例如 14 腳的 7474 (2 個 D 正反器) 與 16 腳的 74175 (4 個 D 正反器), 兩個都是上升緣觸發, 但 74175 只有 /CLR 沒有 /PRE, 而 7474 則都有 :

參考 :

# http://www.nteinc.com/specs/7400to7499/pdf/nte74LS74A.pdf

# http://www.nteinc.com/specs/7400to7499/pdf/nte74LS175.pdf

在序向電路設計中另一個常用的正反器是 JK 正反器, 與 D 正反器採用反相輸入以避免競賽現象不同的是, JK 正反器利用雙重回授與邊緣觸發等技術將 SR latch 中的競賽情況 (例如 NOR latch 中的 S=R=1) 轉變為 Toggle 功能 (狀態交替反轉), 據說命名為 JK 是為了紀念德州儀器公司發明積體電路的工程師 Jack Kilby, 參考 :

# What is the meaning of JK flip flop's J and K ?

不過在探討 JK 正反器之前, 先來看看它的雛型, 也就是雙重回授的 SR latch, 電路圖如下 :

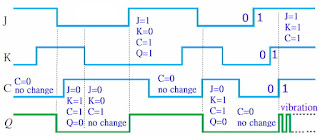

可見這是前面 Gated SR latch 的變形, NAND 閘 G1 與 G2 分別從 /Q 與 Q 輸出回授至其輸入端, 與 SR latch 形成雙重回授, 功能上與上面的 Gated SR latch 一樣, 因此很不幸的, 這個電路有跟競賽一樣麻煩的問題, 就是震盪, 如下面範例波形圖所示 :

在上圖的最後部分, 當 Q=0 (/Q=1), J=K=C=1 時, 因 /Q=1, 因此 G1 閘會輸出 /S=0, 但 G2 閘則會因 Q=0 而仍輸出 /R=1, 這使得後級的 SR latch 被設置為 Q=1, /Q=0, 這個轉態會被回授到第一級的 G1 與 G2, 若這時 J=K=C=1 仍然存在, 則 G1 會因為 /Q=0 回授而輸出 /S=1; 而 G2 則會因為 Q=1 回授而輸出 /R=0, 導致後級 NAND latch 被 reset 為 Q=0 與 /Q=1, 如果 J=K=C=1 的情況一直存在, 則這種因為雙重回授造成的 set-reset-set-reset ... 循環會持續下去而形成震盪.

解決此問題的方法是在 Q 與 /Q 的轉態信號回授到第一級 NAND 閘之前讓 C 回到 low(0) 阻斷回授即可. 一個簡單的方法是使用上面 D 正反器的 Edge detector 電路讓 C 變成 high 位準極短的脈波, 這樣 J=K=1 造成的轉態回授到 G1 與 G2 時 C 已經變成 low(0), 回授被阻斷就不會震盪了, 其電路圖與 function table 如下所示 :

注意, 雖然 J=K=C=1 造成的震盪被阻斷, 但是若 J=K 維持在 high (1), 則下一次上升緣時輸出 Q 會持續轉態 (0 變 1, 1 變 0), 稱為 toggle (交替轉態) 現象, 如下面的範例波形圖所示 :

可見震盪雖然被 edge detector 電路的短脈波阻止了, 但其實這種雙回授電路的震盪本質還是存在, 只是化身為與 CLK 同步的震盪而已. J=K=1 時的 toggle 現象本身就是一種震盪, 可以說它是受到 CLK 規範的震盪, 而上面的雙回授 SR latch 的震盪現象卻是由兩級 NAND 閘之 propagation delay 決定的震盪.

JK 正反器電路符號如下所示 :

上面的 JK 正反器 function table 描述上升緣觸發正反器之功能, 而用於序向電路設計之較一般化的 function table 則如下所示 :

標準 TTL IC 中常用的 JK 正反器例如 74109 (下降緣動作) 與 74112 (上升緣動作), 兩者都是 16 隻腳且都內含兩個具有 /PRE 與 /CLR 的 JK 正反器 :

參考 :

# http://www.nteinc.com/specs/7400to7499/pdf/nte74LS109A.pdf

# http://www.nteinc.com/specs/7400to7499/pdf/nte74LS112A.pdf

最後一種正反器稱為 T 正反器, 它只有一個輸入 T, 當 T=0 時保持狀態不變, 當 T=1 時則轉態, 亦即像 J=K=1 時的 JK 正反器一樣地 toggle, 這也是被稱為 T 正反器的原因. T 正反器常用在計數器, 特別是漣波計數器 (ripple counter) 中. 不過這種正反器並沒有做成標準 IC, 因為它可以用 JK 或 D 正反器製作, 其等效電路圖, function table, 以及範例波形圖, 電路符號如下 :

可見 T 正反器功能非常單純, T=0 時維持狀態不變, 而 T=1 時就 Toggle, 其上下源動作之電路符號如下 :

不考慮觸發型態的話, T 正反器的 function table 如下 :

以上便是在學習序向電路設計之前必須了解的 latch 與 flip-flop 基本知識.

2020-04-25 補充 :

今天找 RLC 串聯電路資料時偶然逛到松山工農林世偉老師的網站, 值得參考 :

# 象棋魂林世偉網站

沒有留言 :

張貼留言